# Урок 4. Триггеры

Ранее были рассмотрены логические элементы, состояние сигнала на выходе которых однозначно определяется состояниями сигналов на входах. В схемах устройств, которые были построены в предыдущих занятиях, сигналы с входов напрямую проходили на выходы и выходные сигналы определялись только комбинацией сигналов на входах. Поэтому такие схемы еще называют комбинационными.

Заметим, что в построенных схемах не были предусмотрены никакие элементы, которые позволяли бы сохранять информацию.

## Моделирование памяти. Триггер

В составе вычислительных устройств и систем управления для хранения информации, представленной в двоичном виде, используют специальные переключательные схемы. Такие схемы принимают одно из двух возможных устойчивых состояний, одно из которых условно принимается соответствующим 1, а другое - соответствующим 0.

**Определение.** Устройство с двумя устойчивыми состояниями, предназначенное для записи и хранения одного бита информации называется **триггером**.

**Триггер** – это целый класс электронных устройств, которые могут длительно находиться в одном из двух устойчивых состояний после прекращения сигнала, меняющего состояние.

Под действием входных сигналов триггер может переключаться из одного состояния в другое. При этом напряжение на его выходах скачкообразно меняется.

Состояние выхода триггера определяется не только сигналами на его входах, но и предыдущим состоянием устройства. Таким образом, триггер является простейшей однобитной ячейкой памяти.

Как правило, триггер имеет два выхода: прямой  $Q$  и инверсный  $\bar{Q}$ . Число входов зависит от выполняемых функций. В зависимости от выполняемой роли входы подразделяют на следующие:

- а) **установочные** – для установки начального состояния триггера;

- б) **информационные** – для ввода информации (установки триггера в определенное состояние);

- в) **исполнительные (синхронизирующие)** – для задания момента срабатывания триггера.

По способу записи информации триггеры делят на **асинхронные и синхронизируемые (тактируемые)**.

В асинхронных триггерах информация может изменяться в любой момент времени при изменении входных сигналов. В синхронизируемых триггерах информация может меняться только в определенные моменты времени, задаваемые дополнительным синхронизирующим сигналом.

## Асинхронный RS-триггер

Существует большое число разнообразных триггеров с различными функциональными возможностями. Однако в основе всех схем лежит самый простой **базовый** (основной) асинхронный RS-триггер.

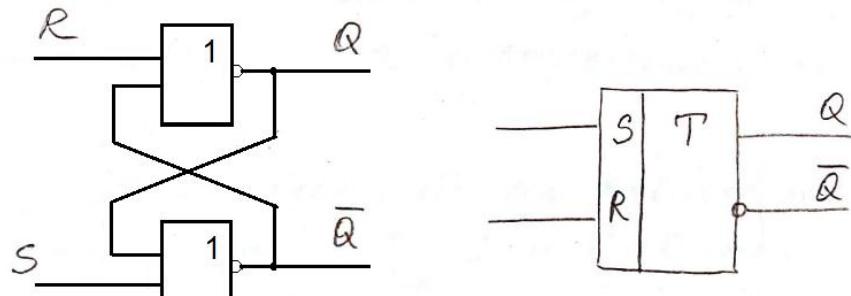

RS-триггер можно получить (построить) из двух логических элементов ИЛИ-НЕ либо двух элементах И-НЕ (см. рис. а) и б)):

рис. а)

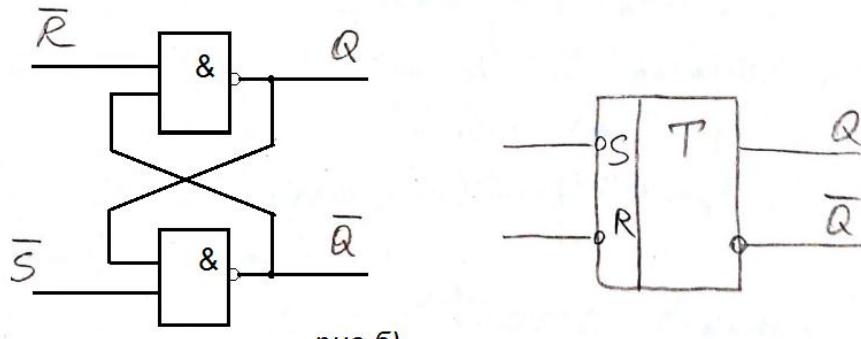

рис б)

Эта схема представляет собой **асинхронный RS-триггер**, в котором элементы охвачены цепями обратных связей, для чего выход каждого элемента подключен к одному из входов другого элемента.

Схемотехническое обозначение триггера приведено на рисунках а) и б) справа, а также на рисунке ниже:

Триггер имеет два входа и два выхода.

| Входы                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| S (set) – установка (обычно установка триггера в 1),<br>R (reset) – сброс (сброс триггера в нулевое состояние).                         |

| Выходы                                                                                                                                  |

| Q (прямой выход) – действующее значение сигнала на прямом выходе триггера<br>$\bar{Q}$ с чертой сверху (инверсный выход триггера, НЕ_Q) |

Как следует из схемы на рис а) при S=1 и R=0 на выходах будет:

$$\begin{aligned}\bar{Q} &= \overline{S+Q} = \overline{1+Q} = 0 \\ Q &= \overline{R+\bar{Q}} = \overline{0+0} = 1\end{aligned}$$

при S=0 и R=1 получим:

$$\begin{aligned}Q &= \overline{R+\bar{Q}} = \overline{1+\bar{Q}} = 0 \\ \bar{Q} &= \overline{S+Q} = \overline{0+0} = 1\end{aligned}$$

При подаче сигнала логического нуля на оба входа триггера, его выходы будут установлены в произвольное состояние. Допустим, Q = 0, а HE\_Q = 1. Если на вход S подать «1», то состояние выхода Q скачкообразно изменится на «1», а HE\_Q - на «0». И это состояние будет поддерживаться в независимости от того «0» или «1» подано на вход S, что и является проявлением свойства памяти.

Соответственно, при подаче уровня «1» на вход R выход Q станет «0», а HE\_Q – «1».

Длительность устанавливающих импульсов может быть очень короткой, и ограничена физическим быстродействием логических модулей, из которых построен триггер.

Ситуация, когда на входах R и S действует высокий уровень, является недопустимой, поскольку при этом схема не может работать корректно. В этом есть недостаток RS-триггера.

Составим таблицу таблицу состояний (переключений, переходов) RS-триггера.

| ВХОДЫ  |   |           |           | ВЫХОДЫ                |                     | Режим работы триггера |

|--------|---|-----------|-----------|-----------------------|---------------------|-----------------------|

| ИЛИ-НЕ |   | И-НЕ      |           | Прямой Q              | инверсный $\bar{Q}$ |                       |

| S      | R | $\bar{S}$ | $\bar{R}$ |                       |                     |                       |

| 0      | 0 | 1         | 1         | $Q_0$                 | $\bar{Q}_0$         | Хранение              |

| 1      | 0 | 0         | 1         | 1                     | 0                   | Запись 1              |

| 0      | 1 | 1         | 0         | 0                     | 1                   | Запись 0              |

| 1      | 1 | 0         | 0         | Запрещенное состояние |                     |                       |

Заметим, что RS-триггеры построенные на двух элементов И-НЕ более распространены. Установка и сброс триггера на элементах 2И-НЕ, в отличие от предыдущего, производится низким уровнем входного сигнала.

Широкому использованию асинхронного RS-триггера в качестве самостоятельного устройства мешают присущие ему существенные недостатки:

- наличие запрещенной комбинации входных сигналов,

- подача информации по двум цепям (R и S),

- низкая помехоустойчивость.

## Синхронный RS-триггер

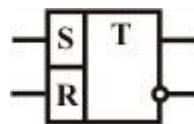

Если к последней схеме добавить еще два вентиля 2И-НЕ, то мы получим синхронный RS-триггер.

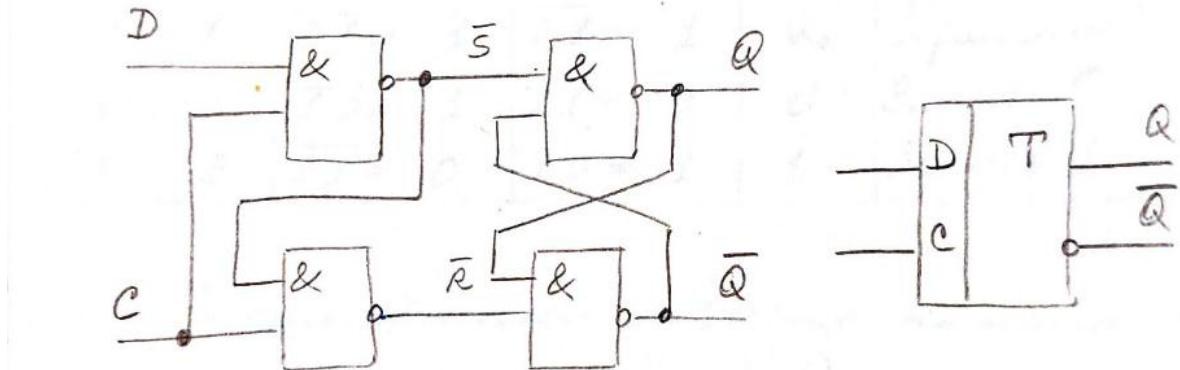

Схема синхронного RS-триггера показана на рисунке:

Изменение состояния такого триггера производится только при воздействии на вход С (Clock) синхронизирующего (тактового) импульса, то есть когда на входе С будет 1.

Синхронный RS-триггер в этом случае работает как RS-триггер.

Если на входе С будет 0, то ни на какие изменения значений входов R и S триггер реагировать не будет.

## Синхронный D-триггер

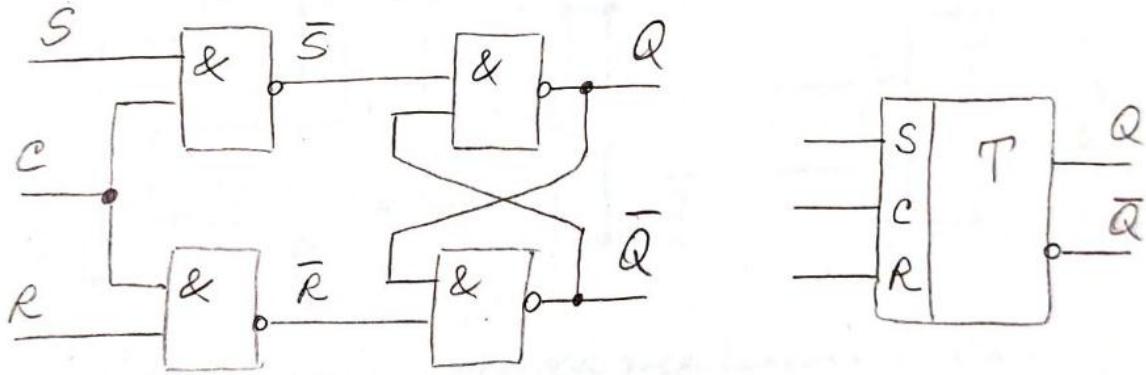

Немного изменив схему синхронного RS-триггера, можно получить D-триггер. (D-delay, задержка).

Синхронный D-триггер свободен от недостатков RS-триггера. Он образуется из RS-триггера и входной комбинационной схемы на двух логических элементах И-НЕ.

Схема D-триггера:

У него только один информационный вход D и вход синхронизации C? задающий момент срабатывания триггера.

Сигналы, предназначенные для записи в триггер поступают на информационный вход D.

Если на этот вход подать «1», а затем подать импульс на вход С, то на выходе Q будет «1», если на вход подать «0», затем импульс на С, то на выходе Q будет «0». Таким образом, D-триггер осуществляет задержку информации, поступающей на вход до окончания того такта, в котором она была записана.

Приведем таблицу состояний D-триггера:

| $C$ | $D$ | $\bar{S} = \bar{C}D$ | $\bar{R} = \bar{C}\bar{S}$ | $Q$   | Режим работы |

|-----|-----|----------------------|----------------------------|-------|--------------|

| 0   | 0   | $\bar{0}\cdot 0 = 1$ | $\bar{0}\cdot 1 = 1$       | $Q_0$ | Хранение     |

| 0   | 1   | $\bar{0}\cdot 1 = 1$ | $\bar{0}\cdot 1 = 1$       | $Q_0$ | Хранение     |

| 1   | 0   | $\bar{1}\cdot 0 = 1$ | $\bar{1}\cdot 1 = 0$       | 0     | Запись 0     |

| 1   | 1   | $\bar{1}\cdot 1 = 0$ | $\bar{1}\cdot 0 = 1$       | 1     | Запись 1     |

При  $C = 0$  D-триггер находится в режиме хранения, при  $C = 1$  – в режиме записи.

Рассмотренный триггер называется **статическим синхронным D-триггером**.

Если сигнал на входе изменится во время действия синхроимпульса, то в триггере окажется записанной та информация, которая предшествовала окончанию синхроимпульса.

Для нормальной работы статического D-триггера необходимо, чтобы изменение информации на D-входе происходило только при  $C = 0$ .

### Динамический синхронный D-триггер

исключает сквозную передачу сигнала с D-входа на выход триггера во время действия синхроимпульса.

В триггере с динамическим управлением информация записывается только в моменты перепада напряжения на входе синхронизации.

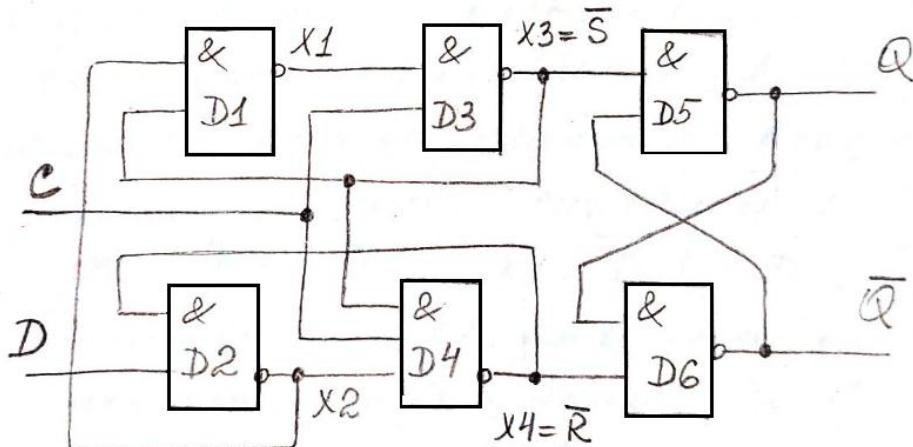

Схема динамического D-триггера:

Условное схемотехническое обозначение:

Рассмотрим работу триггера, учитывая, что в каждый момент времени значения выходных сигналов логических элементов равны:

$$\begin{aligned} X_2 &= \overline{D \cdot X_4}, & X_1 &= \overline{X_2 \cdot X_3}, \\ X_3 &= \overline{C \cdot X_1}, & X_4 &= \overline{C \cdot X_2 \cdot X_3}. \end{aligned}$$

Пока сигнал  $C = 0$ ,  $X_3 = X_4 = 1$ .

Поэтому в паузах между синхроимпульсами выходной триггер находится в режиме хранения информации, а сигналы на выходах первых двух элементов ( $D_1$  и  $D_2$ ) полностью определяются входным информационным сигналом:

$$X_2 = \overline{D \cdot 1} = \overline{D}; \quad X_1 = \overline{\overline{D} \cdot 1} = D$$

Сигналы  $X_1$  и  $X_2$  инверсны по отношению друг к другу, поэтому при появлении  $C = 1$  только один из них разрешает прохождение синхроимпульса через один из элементов  $D_3$  или  $D_4$ :

$C = 1$  и  $D = 1$ , получаем

$$\begin{aligned} \bar{S} &= X_3 = \overline{C \cdot D} = \overline{1 \cdot 1} = 0 \\ \bar{R} &= X_4 = \overline{C \cdot \overline{D} \cdot X_3} = \overline{1 \cdot 0 \cdot 0} = 1 \end{aligned} \quad \left. \begin{array}{l} \text{РЕНИМ} \\ \text{ЗАПИСИ} \\ 1. \end{array} \right\}$$

$C = 1$  и  $D = 0$ , получаем

$$\begin{aligned} \bar{S} &= X_3 = \overline{1 \cdot 0} = 1 \\ \bar{R} &= X_4 = \overline{1 \cdot 1 \cdot 1} = 0 \end{aligned} \quad \left. \begin{array}{l} \text{РЕНИМ} \\ \text{ЗАПИСИ} \\ 0 \end{array} \right\}$$

При изменении информационного сигнала  $D$  во время действия синхроимпульса этот сигнал проходит только на выходы первых элементов и не пропускается элементами  $D_3$  и  $D_4$ .

Таким образом, в динамическом D-триггере нет прямого прохождения сигнала с  $D$ -входа на выход триггера в период действия синхроимпульса.

## Счетный Т-триггер

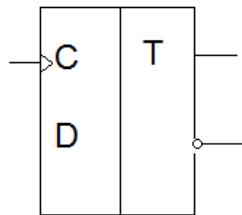

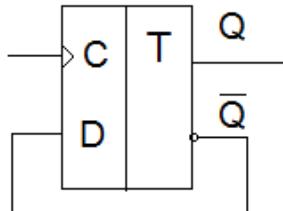

Если информационный вход D в динамическом D-триггере соединить с инверсным выходом HE\_Q (см. рис.), то триггер будет менять свое состояние при каждом изменении состояния входа C от «0» к «1».

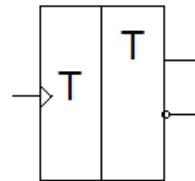

Таким образом получим счетный Т-триггер, который имеет один управляющий вход и два выхода (см. рис.):

Информация на выходах такого триггера меняется на противоположную при каждом положительном перепаде напряжения на счетном входе T.

При изменении от «1» к «0» состояние триггера меняться не будет. Таким образом, частота выходных импульсов будет вдвое меньше частоты входных импульсов. Поэтому данный триггер очень широко используется в цифровой технике в качестве делителя частоты.

Существует большое количество разнообразных триггеров, отличающихся от рассмотренных другой входной логикой. Например известны универсальный D-триггер, DV-триггер с двумя управляющими входами, универсальный JK-триггер и другие.

Интересна разновидность синхронного RS-триггера, не имеющая запрещенной комбинации – универсальный JK-триггер. Он имеет три входа: J (вместо R), K (вместо S), и C. Если на оба информационных входа подана «1», то JK-триггер работает как счетный Т-триггер с входом C.

Отметим, что все виды триггеров основаны на использовании базового асинхронного RS-триггера. Рассмотренные типы триггеров являются основными в сериях интегральных микросхем и позволяют строить на их основе любые цифровые узлы и цифровые автоматы.